2.1.3. DRAM 存取

一支程序使用虚拟地址(virtual address)来选择memory位置。处理器将其转译(translate)成实体地址(physical address),最终由memory控制器选择对应于这个地址的 RAM 晶片。为了选择 RAM 晶片中的个别记忆单元,实体地址的一部分会以数条地址线(address line)的形式被传递进去。

由memory控制器个别定址(address)memory位置是极为不切实际的:4GB 的 RAM 会需要 232 条地址线。作为替代,地址会使用较小的一组地址线,编码成二进位数值传递。以这种方式传递到 DRAM 晶片的地址必须先被多路分解(demultiplex)。有 条地址线的多路分解器(demultiplexer)将会有 2 条输出线(output line)。这些输出线能被用以选择记忆单元。对于小容量的晶片而言,使用这种直接的方法是没什么大问题的。

但假如记忆单元的数量增加,这个方法就不再合适。一个 1Gbit6 容量的晶片将会需要 30 条地址线以及 230 选择线(select line)。在不牺牲速度的前提下,多路分解器的大小会随著输入线(input line)的数量以指数成长。用于 30 条地址线的多路分解器需要大量的晶片空间,外加多路分解器的(尺寸与时间)复杂度。更重要的是,同时在地址线上传输 30 个脉冲(impulse)比「只」传输 15 个脉冲还要难得多。只有少数的地址线能够以长度完全相同或适当安排时间的方式排版。7

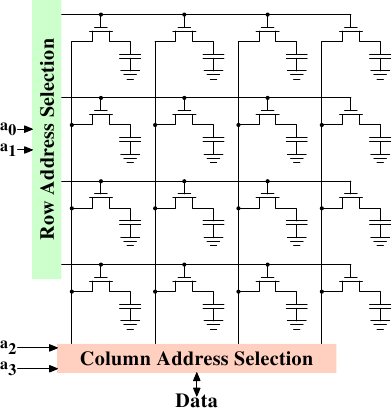

图 2.7 显示了以极高阶角度示意的 DRAM 晶片。DRAM 记忆单元被组织在列(row)与行(column)中。虽然它们可以全都排成一列,但 DRAM 晶片会因而需要一个庞大的多路分解器。借由阵列(array)的方式,便能够以各为一半大小的一个多路分解器与一个多工器达到这种目的。8这从各方面来说都是个大大的节约。在这个例子中,地址线 与 透过行地址选择(row address selection)()9多路分解器选择一整列记忆单元的地址线。在读取时,所有记忆单元的内容都能够被列地址选择(column address selection)多工器(multiplexer)()取得。基于地址线 与 ,其中一行的内容便能够提供给 DRAM 晶片的资料针脚(pin)。这会在许多 DRAM 晶片上平行地发生多次,以产生对应于资料总线宽度的所有位元。

对于写入操作,新的记忆单元的值会被置于资料总线中,然后 ── 当记忆单元借由 与 选取时 ── 储存到资料单元中。相当直观的设计。这实际上有著显然地更多的困难。需要规范发出讯号之后,在资料能够由资料总线读取之前有多少延迟。如同上节所述,电容无法立即充放电。来自于记忆单元的讯号太微弱了,以致于它非得被放大(amplify)不可。对于写入操作,必须指定设置完 与 之后,资料必须在总线维持多久,才能够成功地在记忆单元中储存新值(再提醒一次,电容不会立即被充放电)。这些时间常数(constant)对于 DRAM 晶片的效能而言是至关重要的。我们将会在下一节讨论这些。

一个次要的可扩展性问题是,令 30 条地址线都连接到每个 RAM 晶片也不大可行。一个晶片的针脚是个宝贵的资源。必须尽可能多地平行传输资料(像是一次 64 位元)已经够「糟」。memory控制器必须能够定址每个 RAM 模组(module)(RAM 晶片的集合)。假如因为效能因素,需要平行存取多个 RAM 模组,并且每个 RAM 模组需要它所拥有的一组 30 条或者更多条地址线,那么仅为了处理地址,以 8 个 RAM 模组而言,memory控制器就必须要有多达 240+ 根针脚。

为了克服这些次要的可扩展性问题,DRAM 晶片长期以来必须自行多工地址。这代表地址会被转变成两个部分。由地址位元(图 2.7 的例子中的 与 )组成的第一个部分选取列。这个选择直到撤销之前都会维持有效。接著第二个部分,地址位元 与 ,选取行。决定性的差异在于,只需要两条外部的地址线。译注需要额外一些少量的线路来代表能否取得 与 的线路,但这对于减半地址线来说,这只是个很小的代价。不过,这种地址多工带来了一些自身的问题。我们将会在 2.2 节讨论这些问题。

6. 我厌恶这些 SI 前缀(prefix)。对我来说一个 giga-bit 永远是 230 而非 109 位元。 ↩

7. 现代 DRAM 类型(如 DDR3)可以自动调整时序,但可以容忍的范围有限。 ↩

8. 多工器与多路分解器是对等的,并且这里的多工器在写入时需要如多路分解器一般运作。所以从现在开始我们要忽略其差异。 ↩

9. 名字上的线表示讯号是反相的(negated)。 ↩

译注. 这里的意思单看字面可能比较难理解。以图 2.7 为例,memory由 4 × 4 的记忆单元组成。对外仅提供两条地址线。在选择记忆单元时,首先由两条外部地址线指定列,并将结果暂存起来。接著,再利用同样的两条外部地址线指定行。便能够只用两条外部地址线来指定 16 个记忆单元中的一个。详见 2.2 节。 ↩