2.2.2. 预充电与有效化

图 2.8 未涵盖整个周期。它只显示出存取 DRAM 的完整循环的一部分。在能够发送新的 讯号之前,必须无效化(deactivate)目前锁上的列,并对新的列预充电(precharge)。这里我们仅聚焦在借由明确命令来执行的情况。有些协议上的改进 ── 在某些情况下 ── 能够避免这个额外步骤。不过由预充电引入的延迟仍然会影响操作。

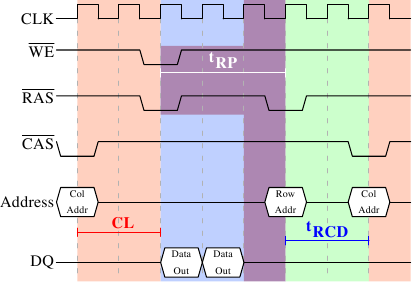

图 2.9 示意从 讯号开始、到另一列的 讯号为止的活动。与先前一样,经过 CL 周期后,便能够取得以第一个 讯号请求的资料。在这个例子中,请求两个字组,其 ── 在一个简易的 SDRAM 上 ── 花了两个周期来传输。也可以想像成是在一张 DDR 晶片上传输四个字组。

即使在命令速率为 1 的 DRAM 模组上,也无法立即发出预充电命令。它必须等待与传输资料一样长的时间。在这个例子中,它花了两个循环。虽然与 CL 相同,但这只是巧合。预充电讯号没有专用的线路;有些实作是借由同时降低允写(Write Enable,)与 的电位来发出这个命令。这个组合本身没什么特别意义(编码细节见 [18])。

一旦发出预充电命令,它会花费 tRP(列预充电时间)个周期,直到列能被选取为止。在图 2.9 中,大部分的时间(以紫色标示)与memory传输时间(浅蓝)重叠。这满好的!但 tRP 比传输时间还长,所以下一个 讯号会被延误一个周期。

假使我们延伸图表的时间轴,我们会发现下一次资料传输发生在前一次停止的 5 个周期之后。这表示在七个周期中,只有两个周期有用到资料总线。将这乘上 FSB 的速度,对 800MHz 总线而言,理论上的 6.4GB/s 就变成 1.8GB/s。这太糟,而且必须避免。在第六节描述的技术能帮忙提升这个数字。程序开发者通常也得尽一份力。

对于 SDRAM 模组,还有一些没有讨论过的时间值。在图 2.9 中,预充电命令受限于资料传输时间。另一个限制是,在 讯号之后,SDRAM 模组需要一些时间才能够为另一列预充电(记作 tRAS)。这个数字通常非常大,为 tRP 值的两到三倍。假如 ── 在 讯号之后 ── 只有一个 讯号,并且资料传输在少数几个周期内就完成,这就是问题。假设在图 2.9 中,起始的 讯号是直接接在 讯号之后,并且 tRAS 为 8 个周期。预充电命令就必须要延迟一个额外的周期,因为 tRCD、CL、与 tRP(因为它比资料传输时间还长)的总和只有 7 个周期。

DDR 模组经常以一种特殊的标记法描述:w-x-y-z-T。举例来说:2-3-2-8-T1。这代表:

| w | 2 | 等待时间(CL) |

| x | 3 | 至 等待时间(tRCD) |

| y | 2 | 预充电(tRP) |

| z | 8 | 有效化至预充电延迟(tRAS) |

| T | T1 | 命令速率 |